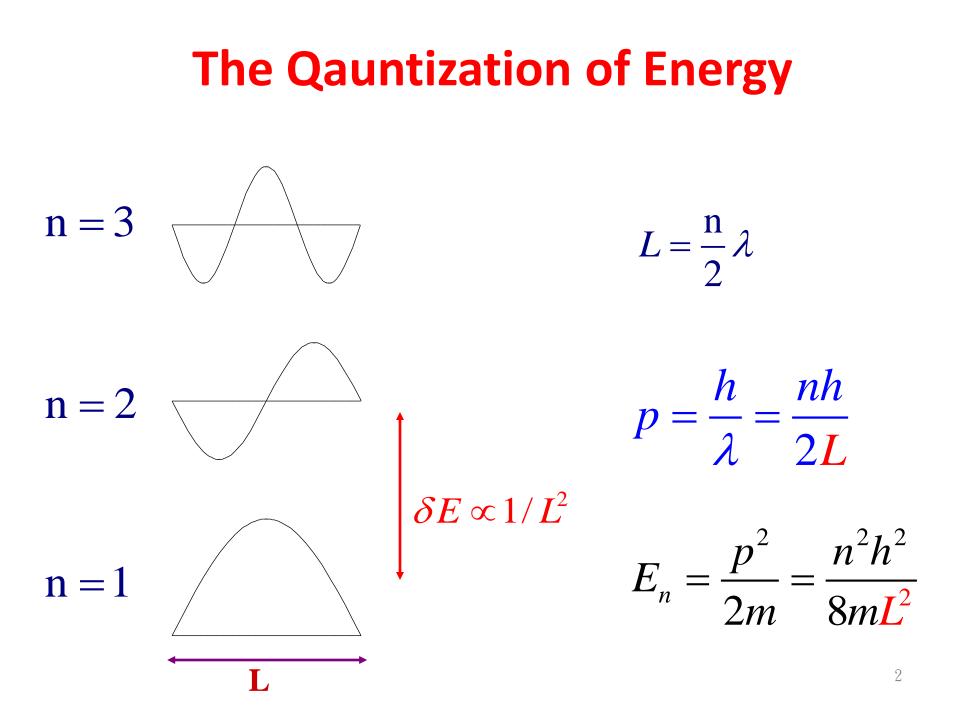

# (II) Quantization

### **Confinement of the materials wave**

### **Standing Wave**

**Quantizations**

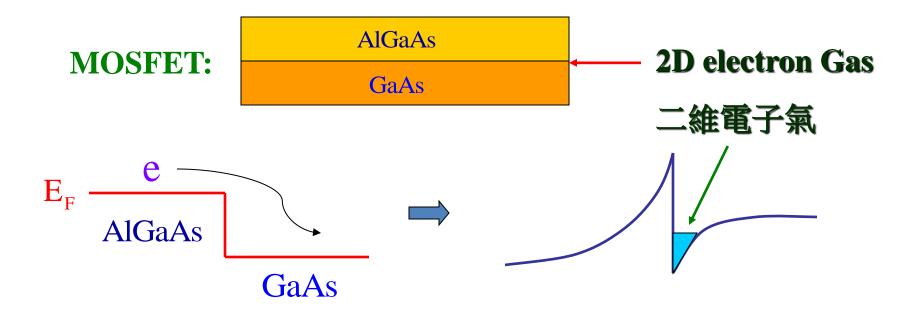

## **Quantum well: 1D confinement**

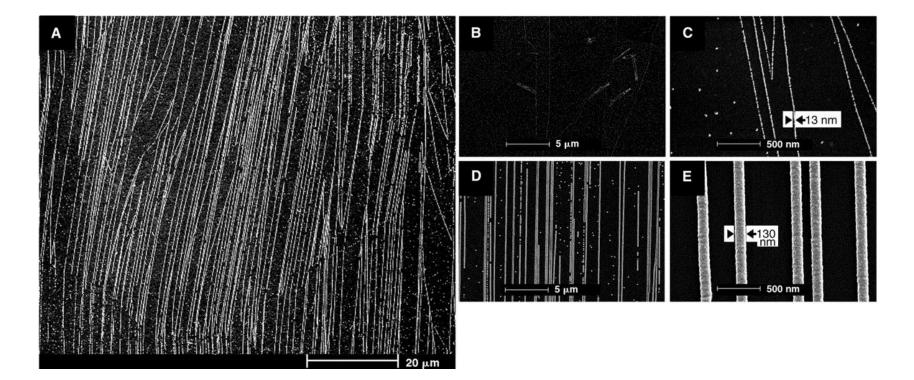

### **Quantum wire: 2 D-Confinement**

SEM images of MoO<sub>x</sub> nanowires on graphite surfaces Science **290**, 2120-2123, (2000)

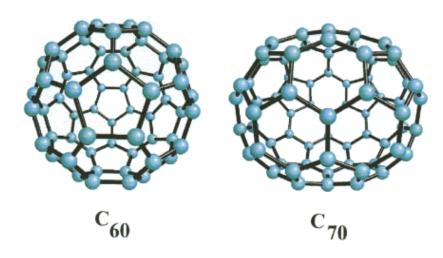

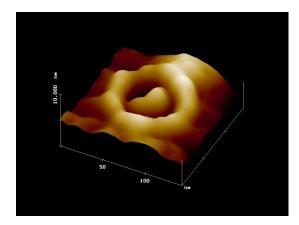

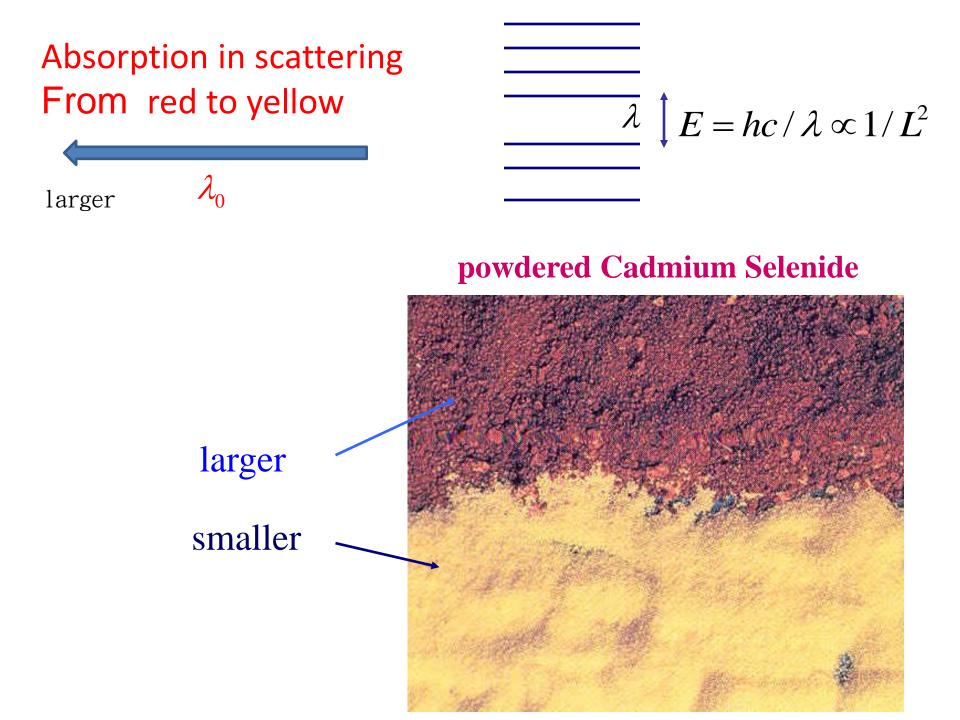

## Quantum dot: 3 D - Confinement

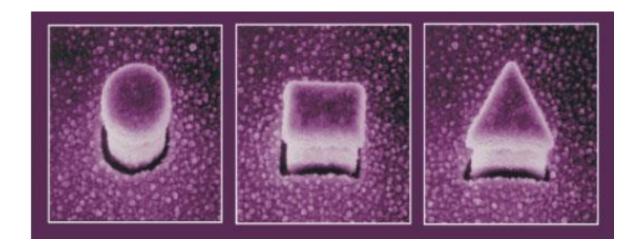

# **Quantum Dots of various shape**

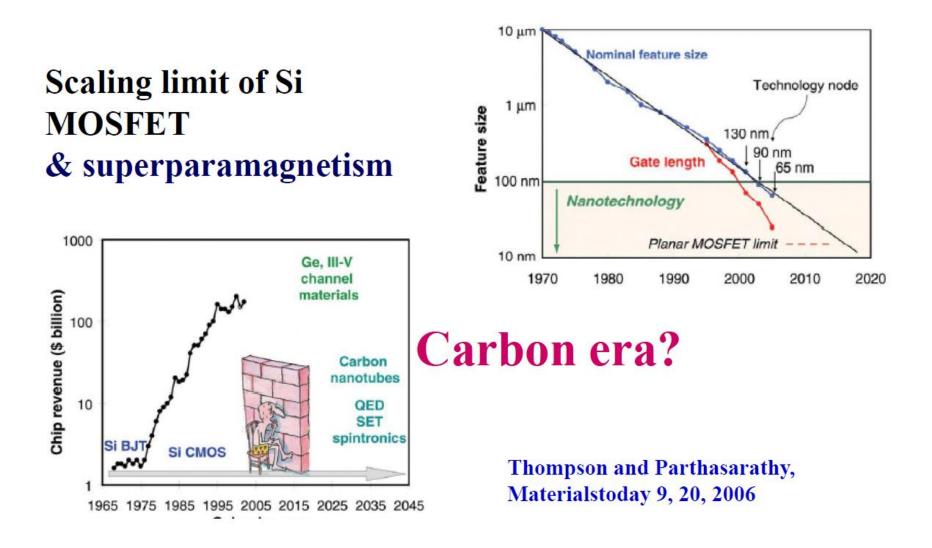

# **Background for search new platform**

# The Advent of Carbon Era?

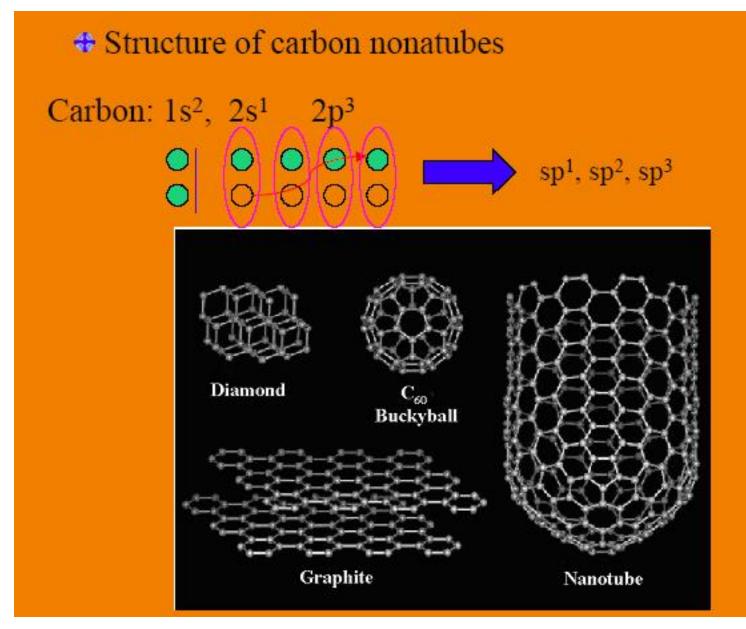

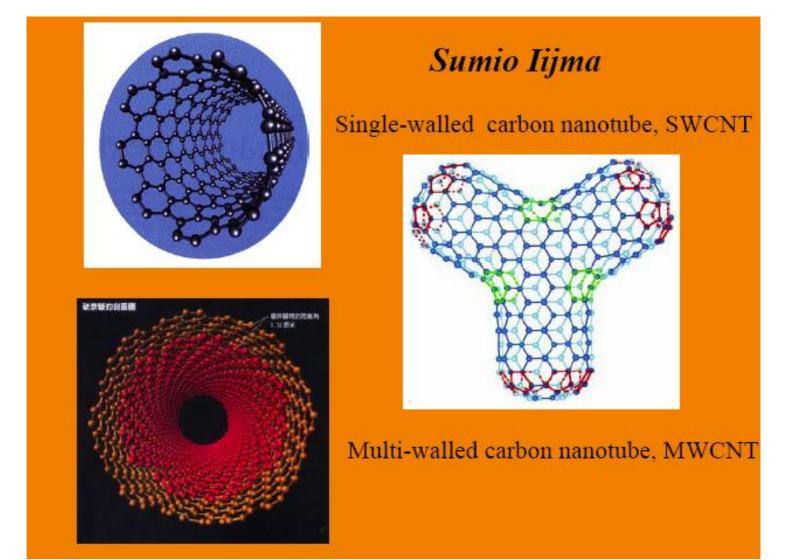

# **Carbon Nanotube**

# **Carbon Nanotube**

### **Carbon Nanotube based Transistors / Electronics**

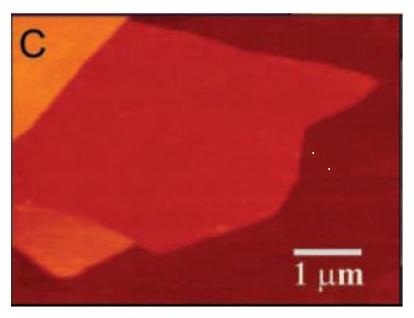

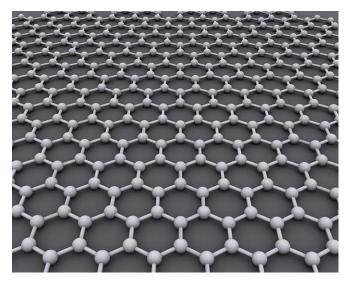

# Unexpected realization of graphene sheet

mechanically exfoliated graphene sheets

AFM image of single-layer graphene on SiO<sub>2</sub> K.S. Novoselove et al., Science 306, 666 (2004)

# (III) Tunneling and Nano-electronics

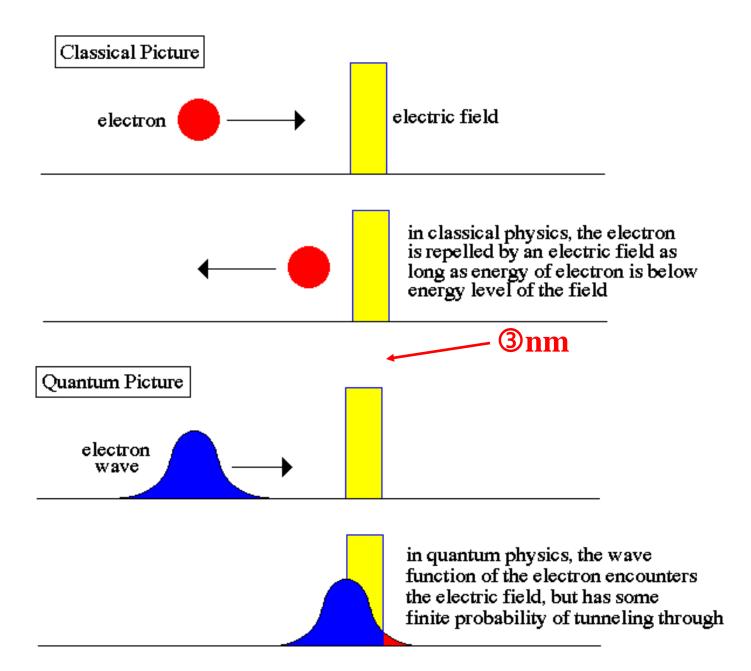

# Quantum Tunneling is the major effect for the failure of Transistor at nano scale

15

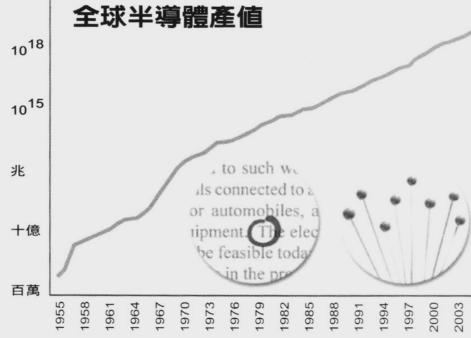

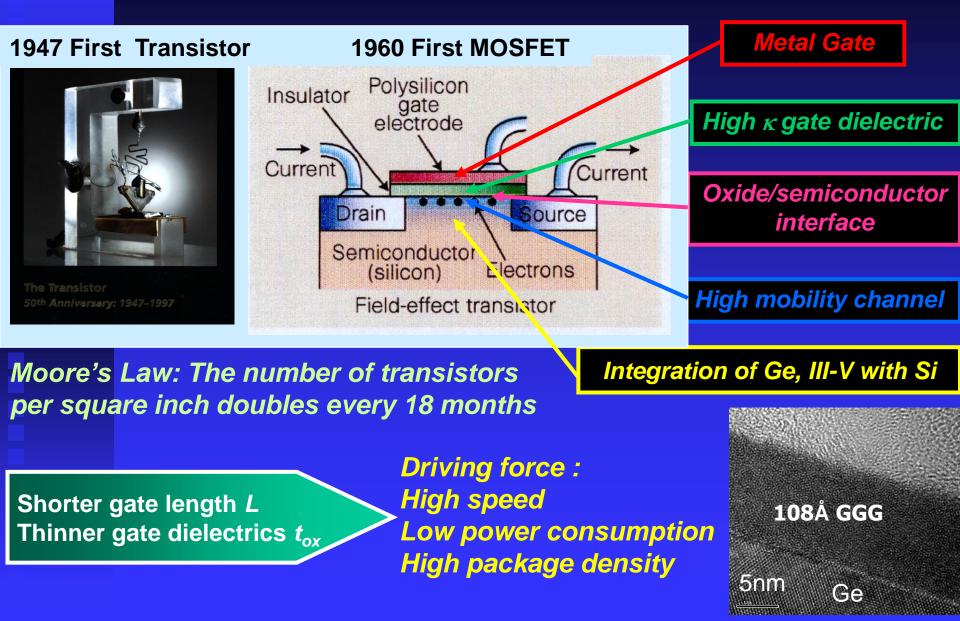

# 近來大力推動奈米科技的背景

# 來自微電子學可能遭遇瓶頸的考慮 Moore's Law: 摩爾定律 A 30% decrease in the size of

printed dimensions every 1.5 years. 矽晶上電子原件數每1年半會增加一倍 全球半導體產值

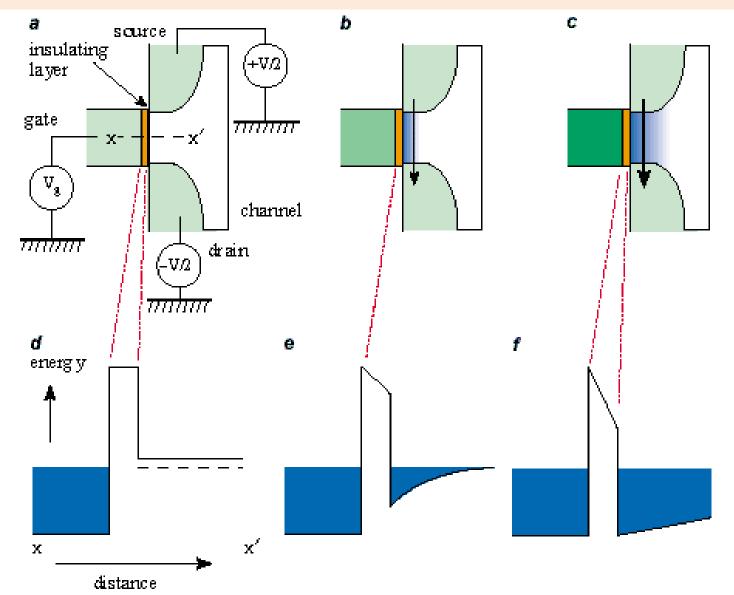

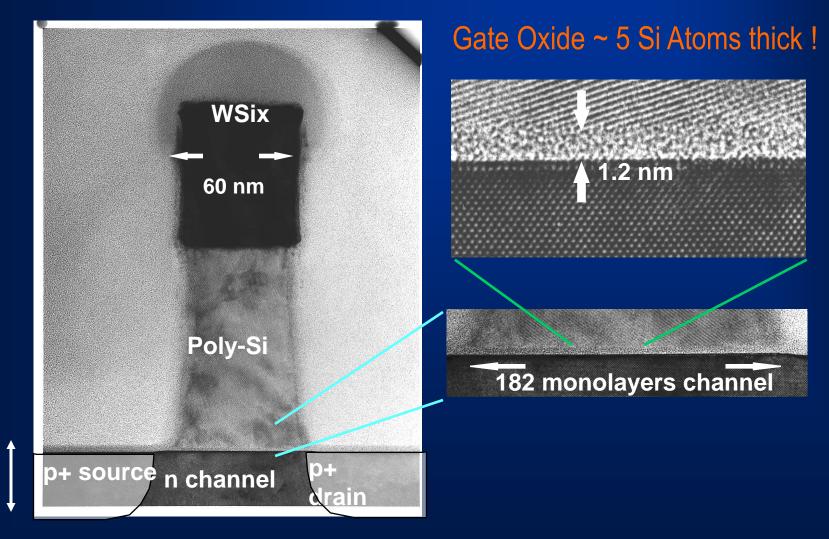

# Scaling Limits to CMOS Technology

Shrinking the junction depth increasing the carrier concentration

**Reliability:** 25 22 18 16 Å processing and yield issue

**Tunneling :** 15 Å

Design Issue: chosen for  $1A/cm^2$  leakage  $I_{on}/I_{off} >> 1$  at 12 Å

#### **Bonding:**

Fundamental Issues---

- how many atoms do we need to get bulk-like properties?

EELS -- Minimal 4 atomic layers !!

- Is the interface electronically abrupt?

- Can we control roughness?

In 1997, a gate oxide was 25 silicon atoms thick.

In 2007, a gate oxide will be 5 silicon atoms thick, if we still use  $SiO_2$

and at least 2 of those 5 atoms will be at the interfaces.

# Fundamental Materials Selection Guidelines

$Si + MO_{x} \longrightarrow M + SiO_{2}$   $Si + MO_{x} \longrightarrow MSi_{2} + SiO_{2}$   $Si + MO_{x} \longrightarrow MSiO_{x} + SiO_{2}$

Thermodynamic stability in contact with Si to 750°C and higher. (Hubbard and Schlom) Alkaline earth oxide, IIIB, IVB oxide and rare earth oxide

- Dielectric constant, band gap, and conduction band offset

- Defect related leakage,

- substantially less than SiO<sub>2</sub> at  $t_{eq} < 1.5$  nm

- Low interfacial state density  $D_{it} < 10^{11} \text{ eV}^{-1} \text{ cm}^{-2}$

- Low oxygen diffusivity

- Crystallization temperature >1000°C

- $t_{eq}$ : equivalent oxide thickness (EOT) to be under 1.0 nm  $t_{eq} = t_{ox} \kappa_{SiO2} / \kappa_{ox}$

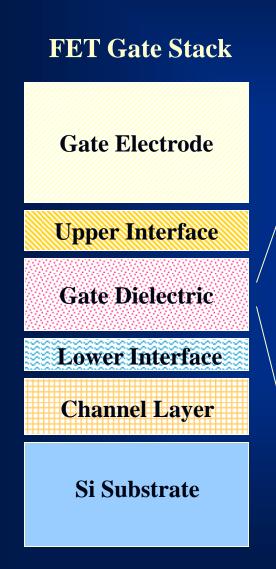

### Integration Issues for High K Gate Stack

### **Critical Integration Issues**

- Morphology dependence of leakage Amorphous vs crystalline films?

- Interfacial structures

- Thermal stability

- Gate electrode compatibility

- Reliability

### **Fundamental Limitations**

- Fixed charge

- Dopant depletion in poly-Si gate

- Dopant diffusion

- Increasing field in the channel region

# **Basic Characteristics of Binary Oxide Dielectrics**

| Dielectrics                                                                                                               | SiO <sub>2</sub>     | Al <sub>2</sub> O <sub>3</sub> | Y <sub>2</sub> O <sub>3</sub> | HfO <sub>2</sub> | $Ta_2O_5$  | ZrO <sub>2</sub>  | La <sub>2</sub> O <sub>3</sub> | TiO <sub>2</sub>  |

|---------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------|-------------------------------|------------------|------------|-------------------|--------------------------------|-------------------|

| Dielectric constant                                                                                                       | 3.9                  | 9.0                            | 18                            | 20               | 25         | 27                | 30                             | 80                |

| Band gap (eV)<br>Band offset (eV)                                                                                         | 9.0<br>3.2           | 8.8<br>2.5                     | 5.5<br>2.3                    | 5.7<br>1.5       | 4.5<br>1.0 | 7.8<br>1.4        | 4.3<br>2.3                     | 3.0<br>1.2        |

| Free energy of formation<br>MO <sub>x</sub> +Si <sub>2</sub> → M+ SiO <sub>2</sub><br>@727C, Kcal/mole of MO <sub>x</sub> | -                    | 63.4                           | 116.8                         | 47.6             | -52.5      | 42.3              | 98.5                           | 7.5               |

| Stability of amorphous phase                                                                                              | High                 | High                           | High                          | Low              | Low        | Low               | High                           | High              |

| Silicide formation ?                                                                                                      | -                    | Yes                            | Yes                           | Yes              | Yes        | Yes               | Yes                            | Yes               |

| Hydroxide formation ?                                                                                                     | -                    | Some                           | Yes                           | Some             | Some       | Some              | Yes                            | Some              |

| Oxygen diffusivity<br>@950C (cm <sup>2</sup> /sec)                                                                        | 2x 10 <sup>-14</sup> | 5x 10 <sup>-25</sup>           | ?                             | ?                | ;          | 10 <sup>-12</sup> | ;                              | 10 <sup>-13</sup> |

### **Si** CMOS Device Scaling – Beyond 22 nm node High κ, Metal gates, and High mobility channel

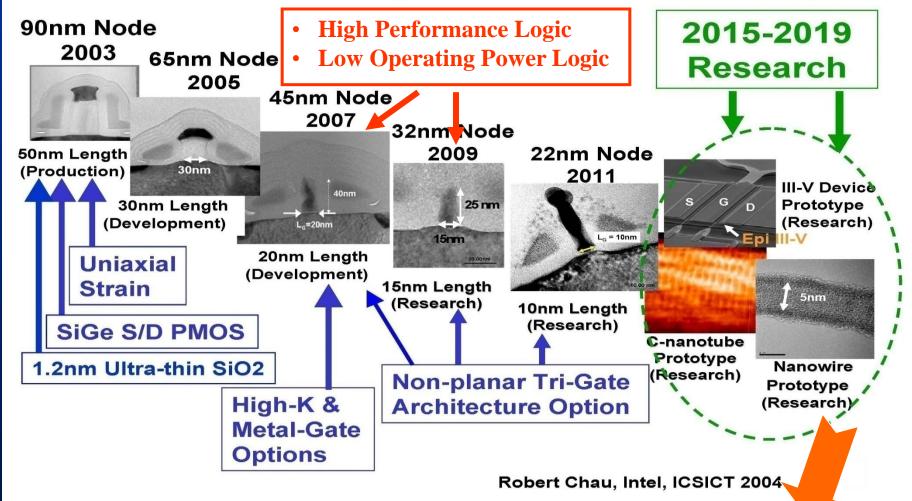

# **Intel Transistor Scaling and Research Roadmap**

#### **Transistor Scaling and Research Roadmap**

#### More non-silicon elements introduced

#### Science and Technology of Ultimate CMOS

#### The Ultimate CMOS – End of road map

#### To achieve higher speed and lower power consumption

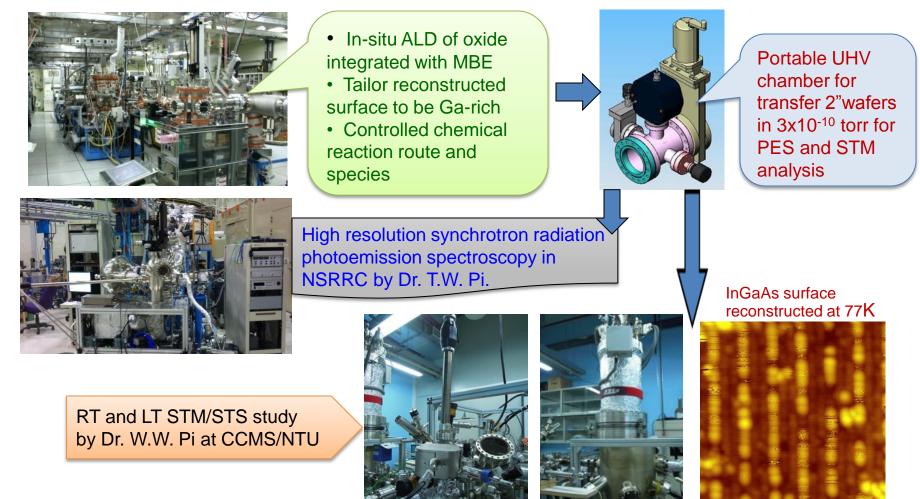

R&D of III-V InGaAs MOSFET state-of-art technology below 7 nm node, by combining advanced analysis of spectroscopy/microscopy/quantum transport/theoretical modeling

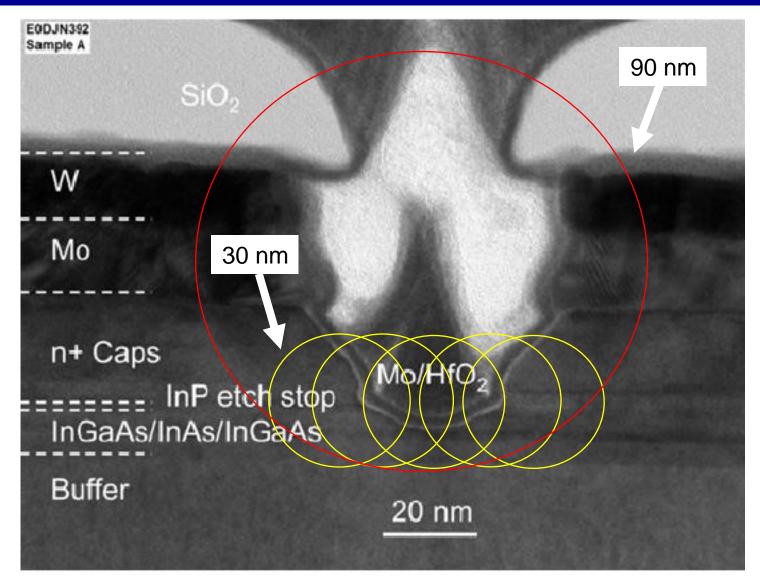

### Bragg Ptychography on III-V MOSFETs with gate length < 30 nm

J. A. Alamo et al., IEDM 24 (2013)

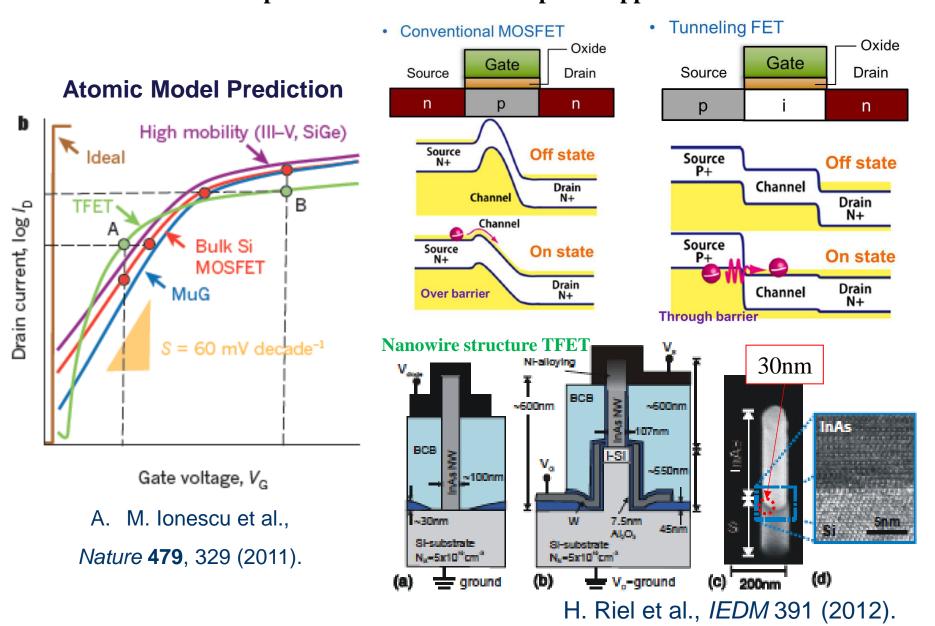

#### **TFETs offer sharper turn-on devices compared to MOSFETs**

**lower VDD to lower Switching Energy (P**active ~C • VDD<sup>2</sup>) Better performance for ultra low-power applications

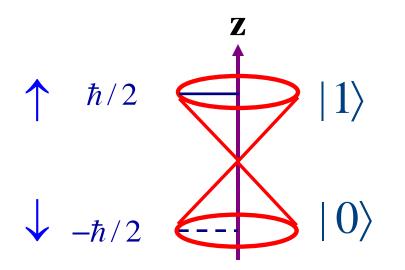

# **(IV) Quantum Spin**

# Spin and Nano technology

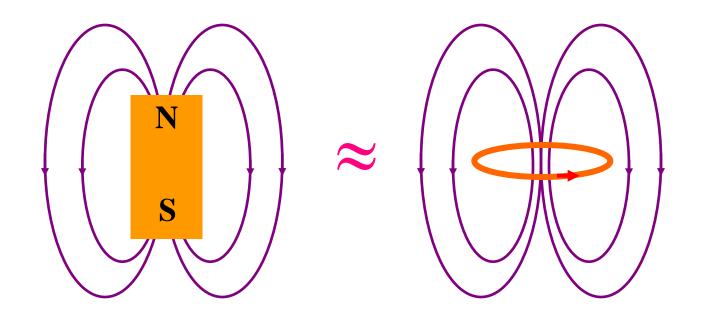

# Electron Spin is the smallest unit of magetism, Came from Quantum Mechanics

# Often being used for magnetic recording ~30 billion market

Well read: spintronics has dramatically increased data storage densities in hard drives.

# Spintronics $\Leftrightarrow$ Electronics

### Magnetic Tunnel Junctions(MTJ)

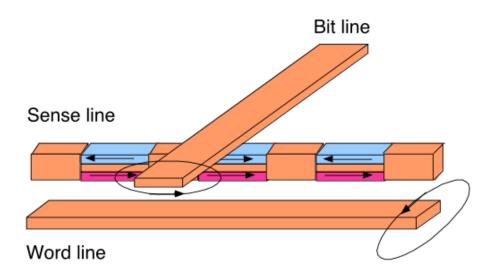

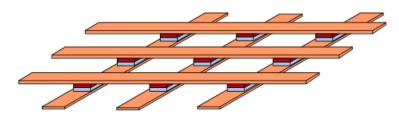

# New generation of computer

### **Compultion and storage in one shot**

**Fig. 7.** A schematic representation of RAM that is constructed of magnetic tunnel junctions connected together in a point contact array. The conducting wires provide current to the junctions and permit voltage measurements to be made. They also enable the manipulation of the magnetization of the elements by carrying currents both above and below the magnetic junctions to create magnetic fields.

When turn-on, it is ready!

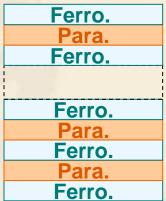

# Giant Magnetoresistance(GMR)

#### What is GMR?

- GMR is a very large change in electrical resistance that is observed in a ferromagnet/paramagnet multilayer structure.

- Resistance change occurs when the relative orientations of the magnetic moments in alternate ferromagnetic layers change as a function of applied field.

The total resistance of this material is lowest when the magnetic orientations of the ferromagnetic layers are aligned, is highest when the orientations are anti-aligned.

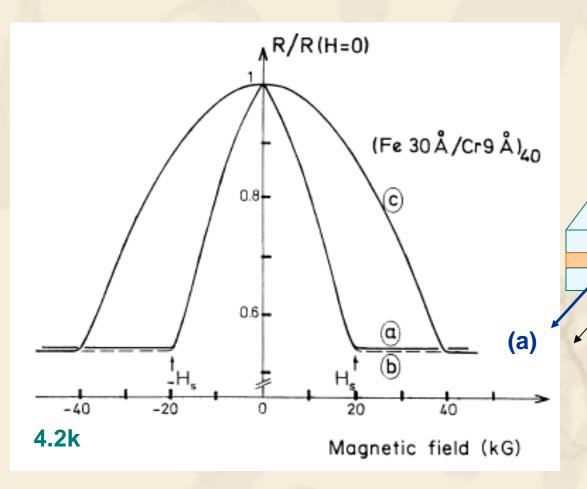

# First Evidence of GMR

Fe **(b)** Fe Hs corresponds to the field at which all layer magnetizations point

**(C)**

along the field direction.

M. N. Baibich, J. M. Broto, A. Fert, F. Nguyen Van Dau, F. Petroff, Phys. Rev. Lett. , 61 , 2472 (1988)

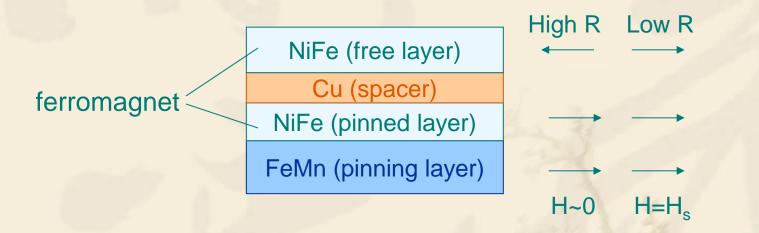

# Spin-Valve GMR \* What is Spin-Valve GMR ?

The simple structure of Spin-valve GMR is

The magnetisation of the top permalloy layer is free to rotate as the field is varied, Second permalloy layer is fixed due to its exchange interaction with the iron-manganese layer.

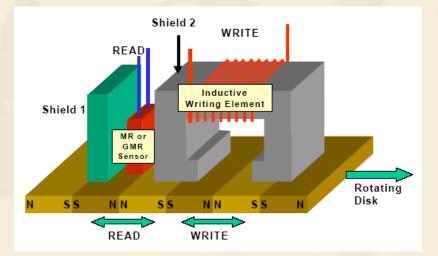

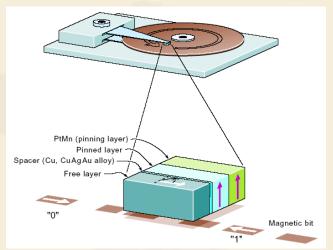

# **GMR Spin Valve Reading Head**

♣ Magnetization is stored as a "0" in one direction and as a "1" in the other. This is the magnetic field sensed by the GMR head.

When the head passes over these magnetic bits, the magnetization direction of the free layer in the head responds to the fields in each bit by rotating either up or down.

The resulting change in the resistance is sensed by the voltage acrossing the GMR head (current passing through the GMR element is constant).

Dr. K. Gilleo, Cookson Electronics ; N. Kerrick and G. Nicholls, AMPM

# Quantum behavior of ferromagnets -Spin as a quantum qubit

$qubit = \alpha | 0 \rangle + \beta | 1 \rangle$

**Due to superposition More information!**

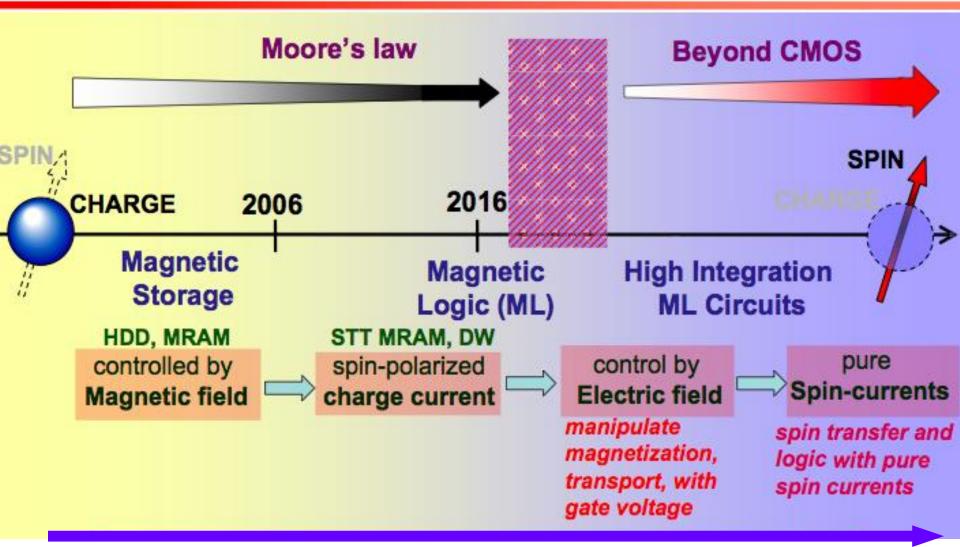

### **Tentative roadmap**

#### Can we take the "charge" out of Spintronics ? To generate pure spin current !

Courtesy Claude Chappert Université Paris Su INTERMAG 2008 Madrid Spain

- Reducing the heat generated in traditional electronics is a major driving force for developing spintronics.

- Spin-based transistors do not strictly rely on the raising or lowering of electrostatic barriers, hence it may overcome scaling limits in charge-based transistors.

- Spin transport in semiconductors may lead to dissipationless transfer of information by pure spin currents.

- Allow computer speed and power consumption to move beyond limitations of current technologies.

## Reliable generation of pure spin currents!

- ✓ Spin Hall effect (2004)

- ✓ Spin Pumping (2006)

- ✓ Inverse Spin Hall effect (2006)

- ✓ Spin Seebeck effect (2008)

- ✓ Spin Caloritronics (2010)

Major Qauntum Effect at the nano scale

Interference

Quantization

Tunneling

Quantum Spin