**Research on III-V and Ge nano-electronics for science and technology beyond Si CMOS**

Minghwei HONG

National Tsing Hua University, Hsinchu, Taiwan

Background on GaAs surface Fermi level unpinning

Interfacial atomic manipulation

■ III-V, GaN, and Ge MOSFET with high  $\kappa$  + metal gates, Spintronics, graphene

32 and 22 nm node Si CMOS (high κ + metal gates)

MBE + ALD for EOT < 1.0 nm</li>

Single crystal oxides on Si, GaN, III-V's and overgrowth of semiconductors

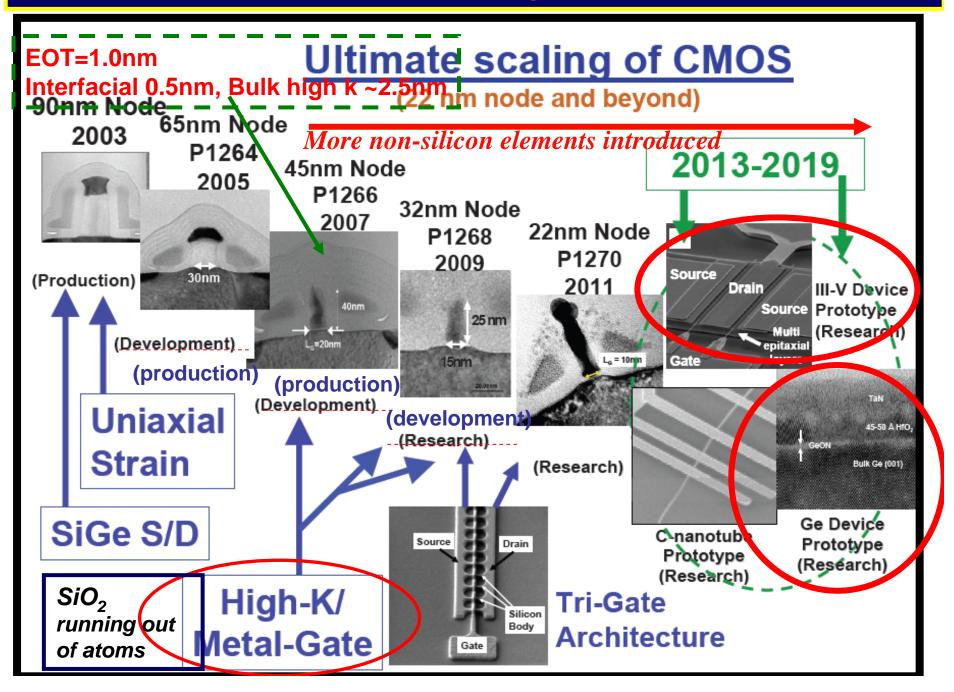

#### Intel (Sematech) Transistor Scaling and Research Roadmap

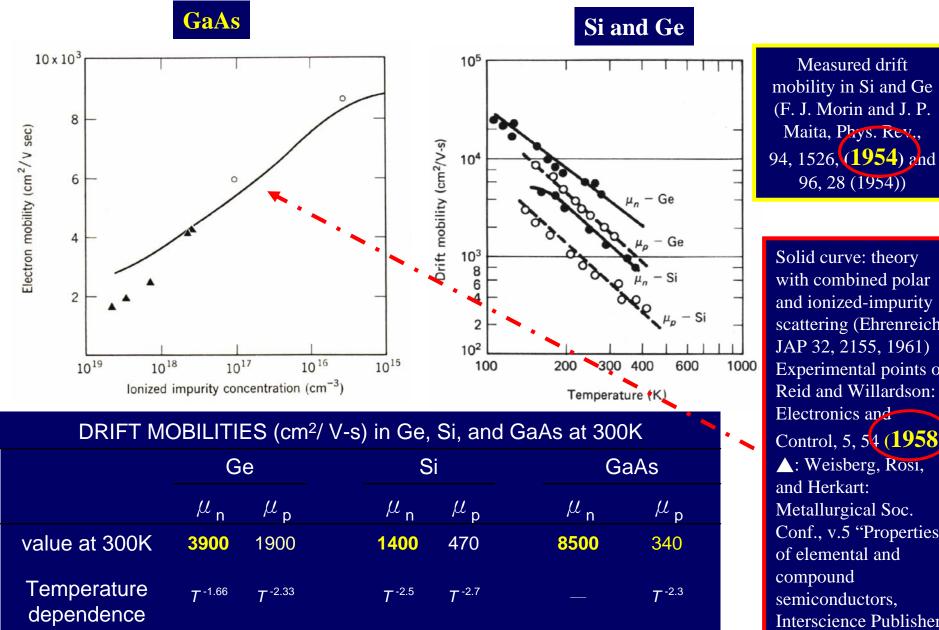

## Electron mobilities in GaAs, Si, and Ge

Solid curve: theory with combined polar and ionized-impurity scattering (Ehrenreich: JAP 32, 2155, 1961) Experimental points o: Reid and Willardson: J. Control, 5, 54 (1958) ▲: Weisberg, Rosi, Metallurgical Soc. Conf., v.5 "Properties Interscience Publishers. New York, p.275

# Do we need a new methodology for GaAs passivation?

A. M. Green and W. E. Spicer Stanford University JVST A11(4), 1061, 1993 Sulfur passivation –Sandroff et al, Bell Labs APL51, 33, 1987 Sb passivation – Cao et al, Stanford Surf. Sci. 206, 413, 1988

"A new methodology for passivating compound semiconductors is presented in which two overlayers are used. In this approach, the first layer defines the surface electronically and the second provides long term protection."

Is it possible to have a III-V (GaAs) MOS, similar to SiO<sub>2</sub>/Si, in which a low  $D_{it}$ , a low electrical leakage current density, thermodynamic stability at high temp. (>800°C), single layer of gate dielectric, no S and Sb, etc are achievable?

**YES**!!!

Is it necessary to have GeON as an interfacial layer in Ge MOS?

#### Pioneering work of GaAs and InGaAs MOSFET's using $Ga_2O_3(Gd_2O_3)$ at Bell Labs with single overlayer

#### • 1994

- novel oxide  $Ga_2O_3(Gd_2O_3)$  to effectively passivate GaAs surfaces

- 1995

- establishment of accumulation and inversion in p- and n-channels in Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>)-GaAs MOS diodes with a low D<sub>it</sub> of 2-3 x 10<sup>10</sup> cm<sup>-2</sup> eV<sup>-1</sup>(IEDM)

#### • 1996

- first e-mode GaAs MOSFETs in p- and n-channels with inversion (IEDM)

- Thermodynamically stable

- 1997

0

e-mode inversion-channel n-InGaAs/InP MOSFET with g<sub>m</sub>= 190 mS/mm, Id = 350 mA/mm, and mobility of 470 cm<sup>2</sup>/Vs (DRC, EDL)

#### 1998

- d-mode GaAs MOSFETs with negligible drain current drift and hysteresis (IEDM)

- e-mode GaAs MOSFETs with improved drain current (over 100 times)

- Dense, uniform microstructures; smooth, atomically sharp interface; low leakage currents

- 1999

- GaAs power MOSFET

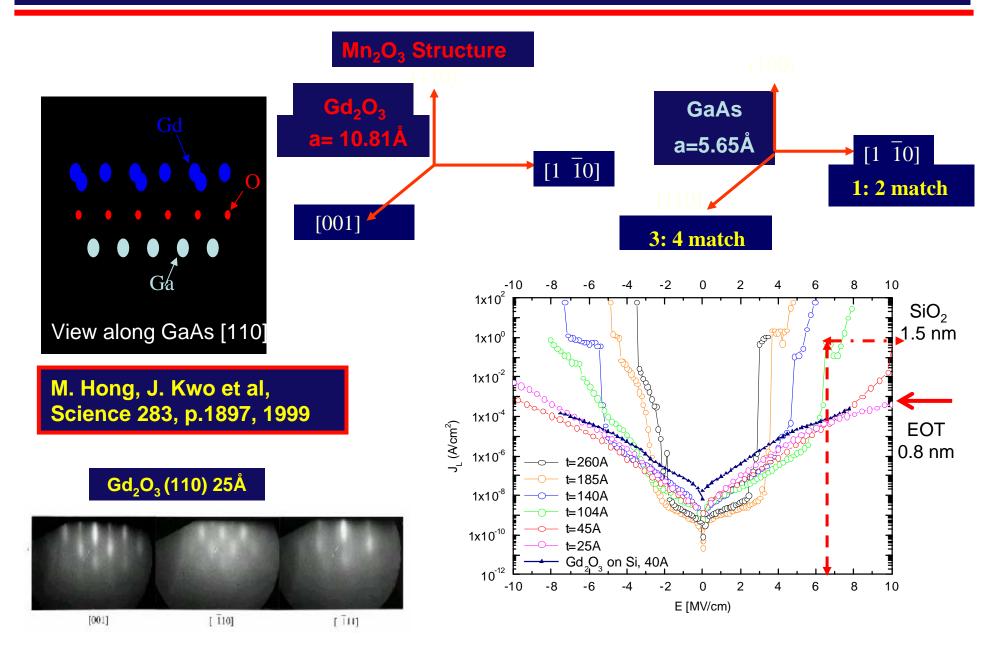

- Single-crystal, single-domain Gd<sub>2</sub>O<sub>3</sub> epitaxially grown on GaAs-

- 2000

### Pioneer Work : Single Domain Growth of (110) Gd<sub>2</sub>O<sub>3</sub> Films on (100) GaAs

|                                    | Si                  | GaAs                              | In <sub>0.53</sub> Ga<br><sub>0.47</sub> As | GaN                 | InAs                | InSb                | units                                                  |

|------------------------------------|---------------------|-----------------------------------|---------------------------------------------|---------------------|---------------------|---------------------|--------------------------------------------------------|

| Energy<br>gap                      | 1.12                | 1.43                              | 0.75                                        | 3.40                | 0.354               | 0.17                | eV                                                     |

| Lattice<br>constant                | 5.431               | 5.65                              | 5.87                                        | 3.19                | 6.06                | 6.50                | Å                                                      |

| Electron<br>effective<br>mass      | 0.19                | 0.063                             | 0.041                                       | 0.20                | 0.023               | 0.014               | -                                                      |

| Electron<br>mobility               | 1500                | 8500                              | 14000                                       | 1300                | 25000               | 78000               | cm <sup>2</sup><br>V <sup>-1</sup> s <sup>-</sup><br>1 |

| Electron<br>saturation<br>velocity | 1 × 10 <sup>7</sup> | <b>2</b> × <b>10</b> <sup>7</sup> | 8 × 10 <sup>6</sup>                         | 3 × 10 <sup>7</sup> | 3 × 10 <sup>7</sup> | 5 × 10 <sup>7</sup> | cm<br>s <sup>-1</sup>                                  |

| Electron<br>mean free<br>path      | 0.07                | 0.15                              | 0.19                                        | 0.2                 | 0.27                | 0.58                | $\mu$ m                                                |

MBE – compound semiconductor growth – A. Y. Cho (National Medal of Science 1993 and National Medal of Technology 2007)

MBE – metal and oxide growth – J. Kwo (first in discovering anti-ferromagnetic coupling through non-magnetic layer in magnetic superlattices PRL's 1985 – 1986)

Frank Shu, UC University Professor and former President of Tsing Hua Univ

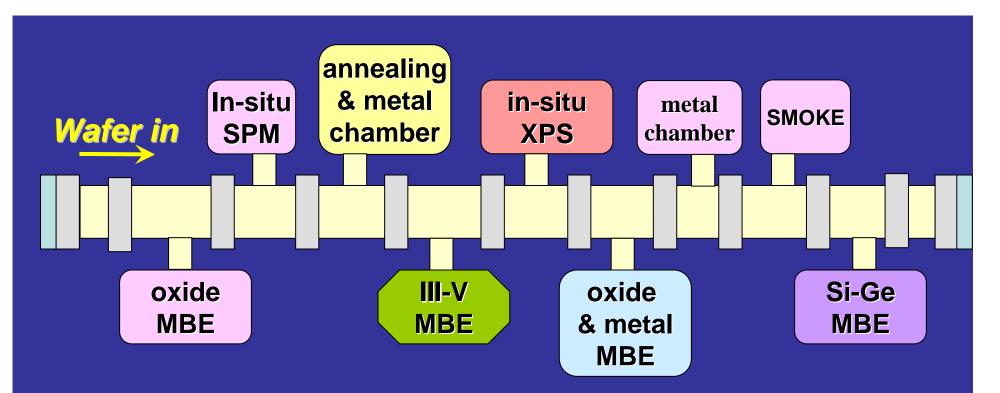

# Multi-chamber MBE/in-situ analysis system

#### **Multichamber Ultrahigh Vacuum System**

- 1. A solid source GaAs-based MBE chamber

- 2. Oxide deposition chamber (As-free)

- 3. Metal chamber

- 4. Ge-Si Chamber

- 5. In-situ XPS

- 6. In-situ SPM

- 7. Other functional chambers, incl.SMOKE

- 8. UHV transfer modules

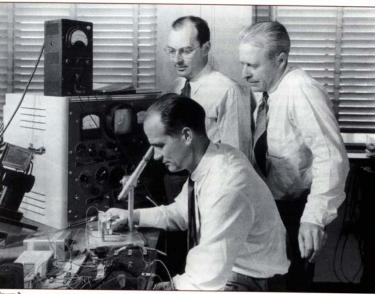

### **1897 J. J. Thomson discovery of electron**

### **1947 The Transistor**

The Transistor 50th Anniversary: 1947-1997

Figure 2.

The three inventors of the transistor: (left to right) William Shockley, John Bardeen, and Walter Brattain, who were awarded the 1956 Nobel Prize in physics.

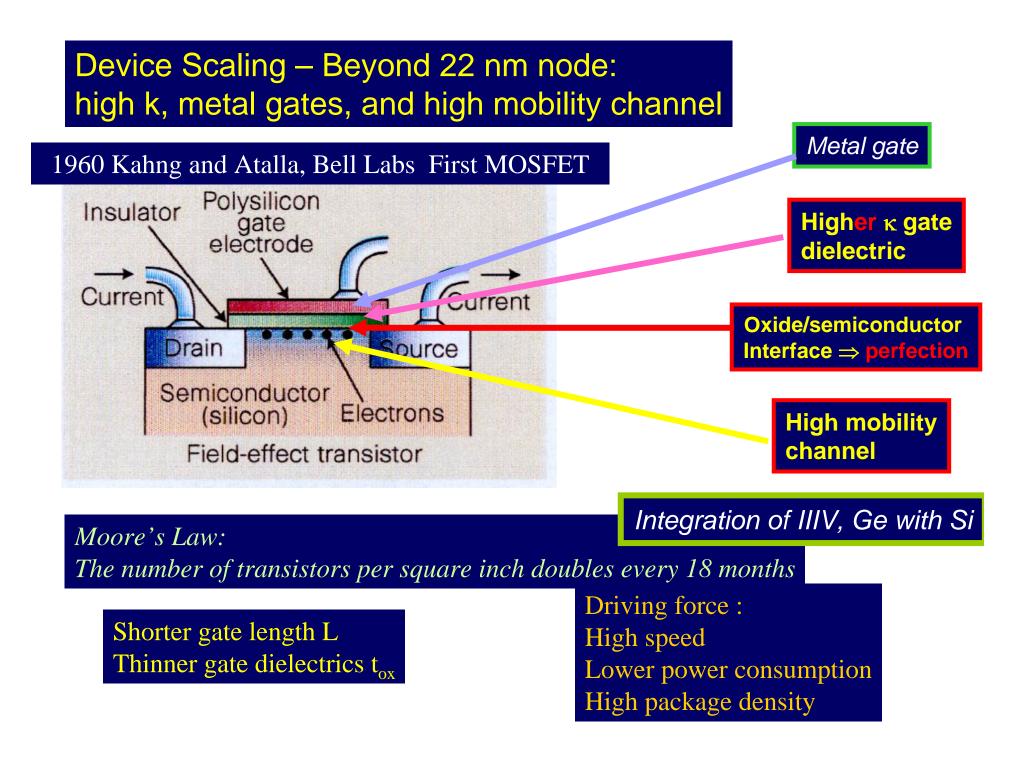

## 2007 High k + metal gate on 45 nm node CMOS

# What next – IIIV, GaN, or Ge MOS in 2017?

Mervin Kelly, the then Director of Res. at Bell Labs, had predicted the problem and had already taken action to find a solution.

Although relays and vacuum tubes were apparently making all things possible in telephony, he had predicted for some years that the low speed of relays and the short life and high power consumption of tubes would eventually limit further progress in telephony and other electronic endeavors.

In the summer of 1945, Kelly had established a research group at Bell Labs to focus on the understanding of semiconductors. The group also had a long-term goal of creating a solid-state device that might eventually replace the tube and the relay.

- Surface Fermi level unpinning in III-V's (the Holy Grail), Ge

- UHV deposited  $Ga_2O_3(Gd_2O_3)$ ; ALD-HfO<sub>2</sub> and  $Al_2O_3$  on InGaAs;  $Ga_2O_3(Gd_2O_3)/Ge$

- Thermodynamic stability of Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>)/III-V's; Ge: temp. limit

- Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>)/InGaAs oxide scalability: EOT scalability

- YDH (yttrium doped HfO<sub>2</sub>) novel high k gate dielectric

- ALD/MBE approach: complete elimination of interfacial layers

- Inversion-channel GaAs-based and GaN MOSFET's

- Single crystal oxides on Si(111)

- GaN/gamma- Al<sub>2</sub>O<sub>3</sub>, Sc<sub>2</sub>O<sub>3</sub>/Si(111); ZnO/- -/Si (111)

- Oxides/GaN

- IETS

- In-situ SPM, SMOKE, XPS

- Spintronics

- Spin LED; Andreev Reflection

- Fe<sub>3</sub>Si/GaAs, magnetic/single crystal oxides/magnetic

- Dilute magnetic Co-HfO<sub>2</sub>

- Spin FET

- InGaAs, GaN, and Ge

- Surface Fermi level unpinning

- Necessity of interfacial layers

- UHV deposited Ga<sub>2</sub>O<sub>3</sub>(Gd<sub>2</sub>O<sub>3</sub>); ALD-HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>

- Electrical characteristics: J-E; C-V; D<sub>it</sub>

- EOT (CET) scalability

- Thermodynamic stability: temp. limit

- Higher k dielectrics

- YDH (yttrium doped HfO<sub>2</sub>) novel high k gate dielectric

- ALD/MBE approach: complete elimination of interfacial layers in Si and Ge

- Inversion-channel InGaAs, Ge, and GaN MOSFET's

- Metal gates

- Integration of InGaAs, Ge, and GaN with Si

- Single crystal oxides on Si(111)

- GaN/gamma- Al<sub>2</sub>O<sub>3</sub>, Sc<sub>2</sub>O<sub>3</sub>/Si(111); ZnO/- -/Si (111)

- Oxides/GaN

- IETS

- In-situ SPM, XPS